- 您现在的位置:买卖IC网 > Sheet目录345 > MT42L256M32D4KP-3 IT:A (Micron Technology Inc)IC LPDDR2 SDRAM 8GBIT 168FBGA

�� �

�

�

�2Gb:� x16,� x32� Mobile� LPDDR2� SDRAM� S4�

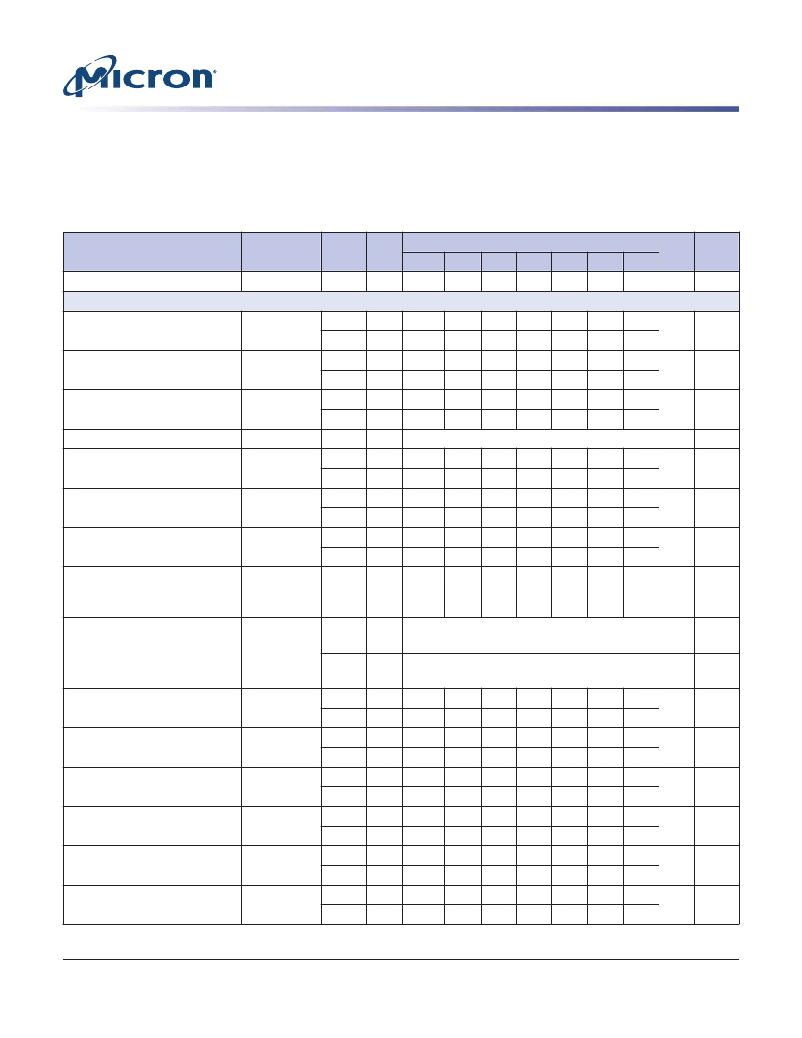

�AC� Timing�

�AC� Timing�

�Table� 86:� AC� Timing�

�Notes� 1–2� apply� to� all� parameters� and� conditions.� AC� timing� parameters� must� satisfy� the� t� CK� minimum� conditions� (in� mul-�

�tiples� of� t� CK)� as� well� as� the� timing� specifications� when� values� for� both� are� indicated.�

�Min/M� t� CK�

�Data� Rate�

�Parameter�

�Maximum� frequency�

�Symbol�

�ax�

�–�

�Min�

�–�

�1066�

�533�

�933�

�466�

�800�

�400�

�667�

�333�

�533�

�266�

�400�

�200�

�333�

�166�

�Unit� Notes�

�MHz�

�Clock� Timing�

�Average� clock� period�

�t� CK(avg)�

�MIN�

�–�

�1.875�

�2.15�

�2.5�

�3�

�3.75�

�5�

�6�

�ns�

�MAX�

�–�

�100�

�100�

�100�

�100�

�100�

�100�

�100�

�Average� HIGH� pulse� width�

�Average� LOW� pulse� width�

�t� CH(avg)�

�t� CL(avg)�

�MIN�

�MAX�

�MIN�

�MAX�

�–�

�–�

�–�

�–�

�0.45�

�0.55�

�0.45�

�0.55�

�0.45�

�0.55�

�0.45�

�0.55�

�0.45�

�0.55�

�0.45�

�0.55�

�0.45�

�0.55�

�0.45�

�0.55�

�0.45�

�0.55�

�0.45�

�0.55�

�0.45�

�0.55�

�0.45�

�0.55�

�0.45�

�0.55�

�0.45�

�0.55�

�t� CK(a�

�vg)�

�t� CK(a�

�vg)�

�Absolute� clock� period�

�t� CK(abs)�

�MIN�

�–�

�t� CK(avg)min�

�±� t� JIT(per)min�

�ps�

�Absolute� clock� HIGH� pulse�

�width�

�Absolute� clock� LOW� pulse�

�width�

�Clock� period� jitter�

�(with� supported� jitter)�

�Maximum� clock� jitter� between�

�t� CH(abs)�

�t� CL(abs)�

�t� JIT(per),�

�allowed�

�t� JIT(cc),�

�MIN�

�MAX�

�MIN�

�MAX�

�MIN�

�MAX�

�MAX�

�–�

�–�

�–�

�–�

�–�

�–�

�–�

�0.43�

�0.57�

�0.43�

�0.57�

�-90�

�90�

�180�

�0.43�

�0.57�

�0.43�

�0.57�

�-95�

�95�

�190�

�0.43�

�0.57�

�0.43�

�0.57�

�-100�

�100�

�200�

�0.43�

�0.57�

�0.43�

�0.57�

�-110�

�110�

�220�

�0.43�

�0.57�

�0.43�

�0.57�

�-120�

�120�

�240�

�0.43�

�0.57�

�0.43�

�0.57�

�-140�

�140�

�280�

�0.43�

�0.57�

�0.43�

�0.57�

�-150�

�150�

�300�

�t� CK(a�

�vg)�

�t� CK(a�

�vg)�

�ps�

�ps�

�two� consectuive� clock� cycles�

�(with� supported� jitter)�

�allowed�

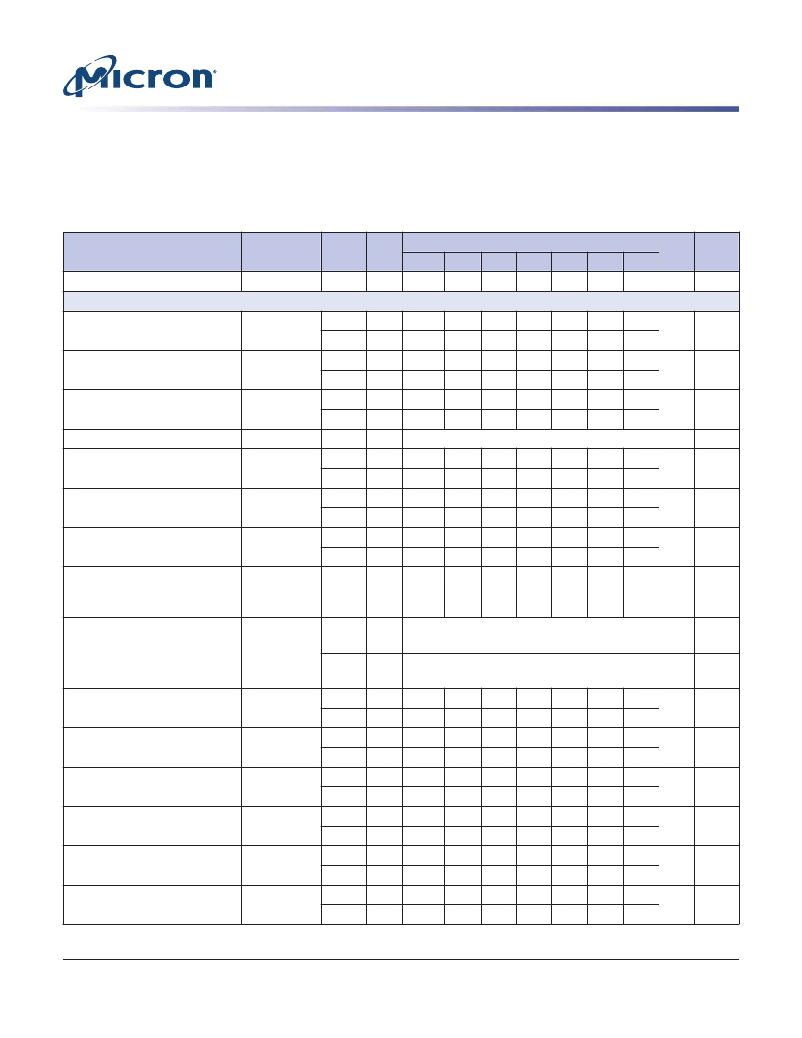

�Duty� cycle� jitter�

�(with� supported� jitter)�

�t� JIT(duty),�

�allowed�

�MIN�

�–�

�MIN� ((� t� CH(abs),min� -� t� CH(avg),min),�

�(� t� CL(abs),min�

�-� t� CL(avg),min))� � t� CK(avg)�

�ps�

�MAX�

�–�

�MAX� ((� t� CH(abs),max� -� t� CH(avg),max),�

�(� t� CL(abs),max�

�-� t� CL(avg),max))� � t� CK(avg)�

�Cumulative� errors� across� 2� cy-�

�cles�

�Cumulative� errors� across� 3� cy-�

�cles�

�Cumulative� errors� across� 4� cy-�

�cles�

�Cumulative� errors� across� 5� cy-�

�cles�

�Cumulative� errors� across� 6� cy-�

�cles�

�Cumulative� errors� across� 7� cy-�

�cles�

�t� ERR(2per),�

�allowed�

�t� ERR(3per),�

�allowed�

�t� ERR(4per),�

�allowed�

�t� ERR(5per),�

�allowed�

�t� ERR(6per),�

�allowed�

�t� ERR(7per),�

�allowed�

�MIN�

�MAX�

�MIN�

�MAX�

�MIN�

�MAX�

�MIN�

�MAX�

�MIN�

�MAX�

�MIN�

�MAX�

�–�

�–�

�–�

�–�

�–�

�–�

�–�

�–�

�–�

�–�

�–�

�–�

�-132�

�132�

�-157�

�157�

�-175�

�175�

�-188�

�188�

�-200�

�200�

�-209�

�209�

�-140�

�140�

�-166�

�166�

�-185�

�185�

�-199�

�199�

�-211�

�211�

�-221�

�221�

�-147�

�147�

�-175�

�175�

�-194�

�194�

�-209�

�209�

�-222�

�222�

�-232�

�232�

�-162�

�162�

�-192�

�192�

�-214�

�214�

�-230�

�230�

�-244�

�244�

�-256�

�256�

�-177�

�177�

�-210�

�210�

�-233�

�233�

�-251�

�251�

�-266�

�266�

�-279�

�279�

�-206�

�206�

�-245�

�245�

�-272�

�272�

�-293�

�293�

�-311�

�311�

�-325�

�325�

�-221�

�221�

�-262�

�262�

�-291�

�291�

�-314�

�314�

�-333�

�333�

�-348�

�348�

�ps�

�ps�

�ps�

�ps�

�ps�

�ps�

�PDF:� 09005aef83f3f2eb�

�2gb_mobile_lpddr2_s4_g69a.pdf� –� Rev.� N� 3/12� EN�

�142�

�Micron� Technology,� Inc.� reserves� the� right� to� change� products� or� specifications� without� notice.�

�2010� Micron� Technology,� Inc.� All� rights� reserved.�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MT45W1MW16BDGB-708 AT

IC PSRAM 16MBIT 104MHZ 54VFBGA

MT48H32M16LFB4-75B IT:C

IC SDRAM 512MB 54VFBGA

MT48H8M16LFB4-75 IT:K TR

IC SDRAM 128MBIT 133MHZ 54VFBGA

MTC100-JA2-P34

CONTACT INSERT PIN

MX841BE

IC CONVERTER WHITE LED 8-SOIC

MXHV9910BTR

IC LED DRIVER HIGH BRIGHT 8-SOIC

MXN12FB12F

MOTOR BRUSHED DC 12V 2922RPM

MXN13FB08B1

MOTOR BRUSHED DC 8V 4714RPM

相关代理商/技术参数

MT42L256M32D4KP-MS

制造商:Micron Technology Inc 功能描述:256MX32 LPDDR2 PLASTIC IND TEMP GREEN WFBGA 1.2V - Bulk